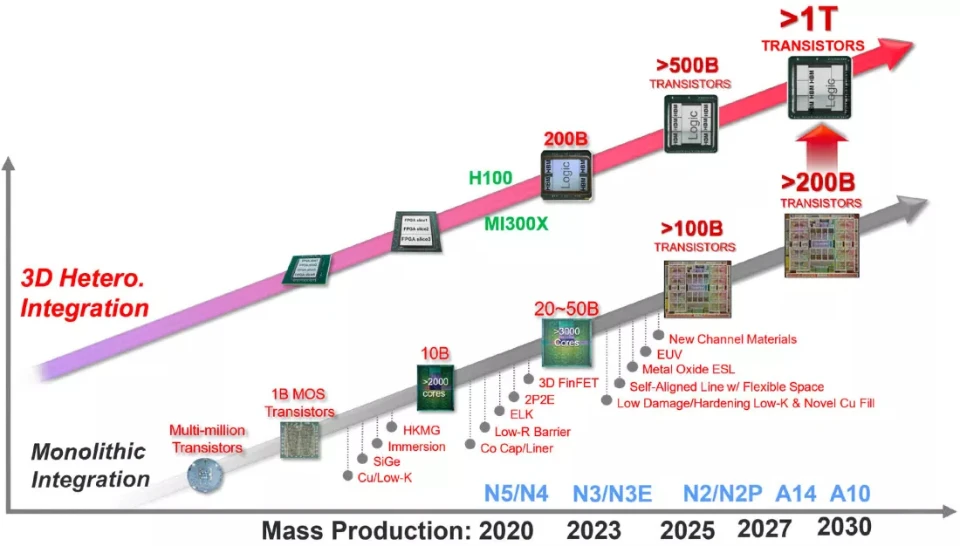

Techspot 에 따르면, TSMC는 최근 IEDM 컨퍼런스에서 차세대 반도체 제조 공정에 대한 제품 로드맵을 발표했습니다. 이 로드맵은 궁극적으로 단일 칩 패키지에 1조 개의 트랜지스터를 집적한 다중 3D 적층 칩렛 디자인을 제공할 것입니다. CoWoS, InFO, SoIC와 같은 패키징 기술의 발전을 통해 TSMC는 이러한 목표를 달성할 수 있을 것이며, 2030년까지 모놀리식 디자인의 트랜지스터 수가 2,000억 개에 달할 것으로 예상합니다.

TSMC, 2030년까지 1nm 칩 생산 가능

엔비디아의 800억 개의 트랜지스터를 탑재한 GH100은 시중에서 가장 복잡한 모놀리식 칩 중 하나입니다. 그러나 이러한 칩의 크기가 커지고 가격이 상승함에 따라 TSMC는 제조업체들이 AMD의 최근 출시된 Instinct MI300X와 인텔의 1,000억 개의 트랜지스터를 탑재한 폰테 베키오와 같은 멀티칩릿 아키텍처를 채택할 것으로 예상합니다.

현재 TSMC는 2nm N2 및 N2P 제조 공정과 1.4nm A14 및 1nm A10 칩 개발을 계속 진행할 예정입니다. TSMC는 2025년 말까지 2nm 생산을 시작할 계획입니다. 2028년에는 1.4nm A14 공정으로 전환하고, 2030년에는 1nm 트랜지스터를 생산할 예정입니다.

한편, 인텔은 2nm(20A) 및 1.8nm(18A) 공정을 개발 중이며, 두 공정 모두 같은 시기에 출시될 예정입니다. 이 새로운 기술의 장점 중 하나는 더 높은 로직 밀도, 향상된 클럭 속도, 그리고 더 낮은 누설 전류를 제공하여 더욱 에너지 효율적인 설계를 가능하게 한다는 것입니다.

TSMC의 차세대 첨단 칩 개발 목표

세계 최대 파운드리 기업인 TSMC는 자사 제조 공정이 인텔 제품보다 성능이 우수할 것이라고 확신합니다. TSMC CEO CC 웨이는 실적 발표 컨퍼런스 콜에서 내부 검토 결과 N3P 기술의 개선이 확인되었으며, TSMC의 3nm 제조 공정은 인텔의 18A 공정과 "비교 가능한 PPA"를 달성했다고 밝혔습니다. 그는 N3P가 더욱 우수하고 경쟁력이 높으며 상당한 비용 우위를 점할 것으로 예상합니다.

한편, 인텔 CEO 팻 겔싱어는 자사의 18A 제조 공정이 1년 전 출시된 TSMC의 2nm 칩보다 성능이 우수할 것이라고 주장했습니다. 물론, 결과는 시간이 지나봐야 알 수 있겠죠.

[광고_2]

소스 링크

![[사진] 동나이성과 호치민시를 연결하는 도로는 5년간의 공사 끝에 아직 미완성 상태다.](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762241675985_ndo_br_dji-20251104104418-0635-d-resize-1295-jpg.webp)

![[사진] 2025-2030년 기간의 Nhan Dan 신문 애국모범대회 전경](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762252775462_ndo_br_dhthiduayeuncbaond-6125-jpg.webp)

![[사진] 까마우, 올해 최고 조수에 대처 "힘들게"…경계 수준 3 넘어설 듯](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762235371445_ndo_br_trieu-cuong-2-6486-jpg.webp)

![[사진] 호치민시 청소년, 깨끗한 환경을 위해 행동하다](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762233574890_550816358-1108586934787014-6430522970717297480-n-1-jpg.webp)

댓글 (0)