Menurut PhoneArena , TSMC dan Samsung Foundry dijangka mula menghasilkan cip 2nm secara besar-besaran pada tahun 2025, yang bermaksud bahawa cip 1.8nm akan membolehkan Intel menerajui proses pembuatan cip. Intel dikatakan membelanjakan antara $300 juta dan $400 juta untuk setiap mesin EUV High-NA.

Setiap mesin ASML High-NA berharga sekurang-kurangnya $300 juta.

"Kami menghantar sistem High-NA yang pertama dan mengumumkannya dalam siaran media sosial. Sistem ini akan dihantar kepada Intel seperti yang dirancang seperti yang diumumkan sebelum ini," kata ASML mengenai pemindahan itu.

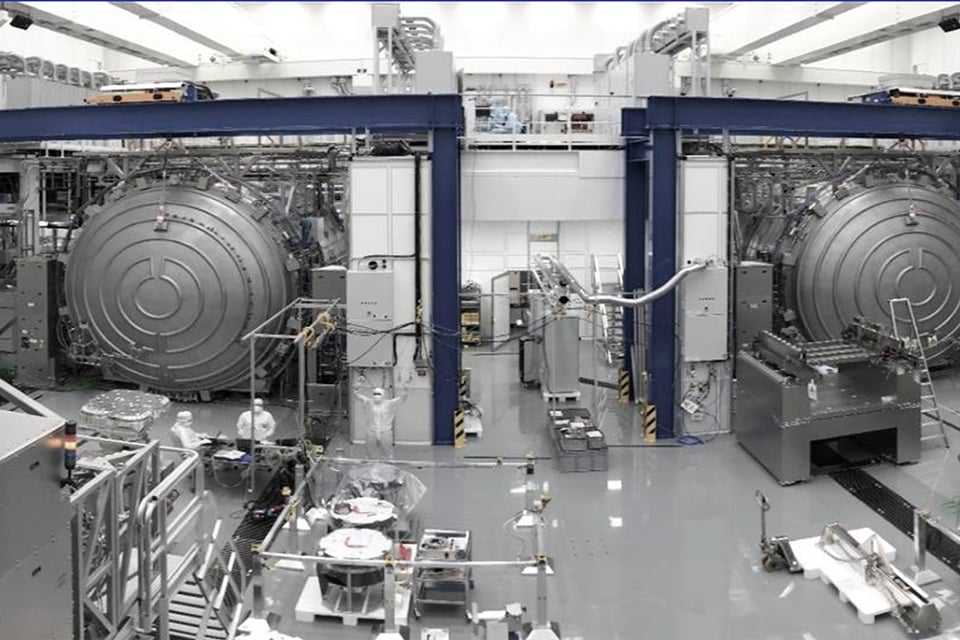

Dengan sistem High-NA, semakin tinggi nombor NA, semakin tinggi resolusi corak yang terukir pada wafer silikon. Walaupun mesin EUV semasa mempunyai apertur .33 (bersamaan dengan resolusi 13nm), mesin High-NA mempunyai apertur .55 (bersamaan dengan resolusi 8nm). Dengan corak resolusi yang lebih tinggi dipindahkan ke wafer, faundri mungkin tidak perlu menjalankan wafer melalui mesin EUV dua kali untuk menambah ciri tambahan, menjimatkan masa dan wang.

Mesin EUV High-NA memberi tumpuan terutamanya kepada mengurangkan saiz transistor dan meningkatkan ketumpatan untuk membungkus lebih banyak transistor di dalam cip. Lebih tinggi bilangan transistor pada cip, lebih berkuasa dan cekap tenaga. Dengan mesin High-NA, transistor boleh dikecilkan 1.7 kali dengan peningkatan ketumpatan 2.9 kali ganda.

Setiap mesin High-NA dihantar oleh ASML dalam 13 bekas besar

Versi baharu mesin High-NA EUV akan membantu menjadikan cip 2nm dan ke bawah mungkin. Baru minggu lepas, TSMC dan Samsung Foundry menangani peta jalan pasca-2nm mereka. Kedua-dua merancang untuk membangunkan semikonduktor menggunakan proses 1.4nm menjelang 2027. Pengeluaran cip 2nm dijangka bermula pada 2025, dan beberapa hari lalu, TSMC membenarkan Apple menilai prototaip cip 2nm.

Mengangkut mesin EUV High-NA bukanlah tugas yang mudah kerana ia dibahagikan kepada 13 kontena besar dan 250 peti. Pemasangan mesin itu juga amat sukar.

Pautan sumber

![[Foto] Memotong bukit untuk memberi laluan kepada orang ramai melalui laluan 14E yang mengalami tanah runtuh](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/08/1762599969318_ndo_br_thiet-ke-chua-co-ten-2025-11-08t154639923-png.webp)

![[Foto] "Kuburan kapal" di Teluk Xuan Dai](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/08/1762577162805_ndo_br_tb5-jpg.webp)

![[Video] Monumen Hue dibuka semula untuk mengalu-alukan pelawat](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/11/05/1762301089171_dung01-05-43-09still013-jpg.webp)

Komen (0)