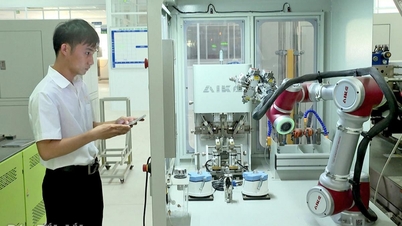

이 연구는 베트남 국립대학교 하노이 정보기술원 산하 마이크로칩 설계 및 응용 연구 센터(SISLAB)의 지능형 통합 시스템 연구 그룹(SISLAB)의 연구 결과입니다. 이 연구는 생산 전 설계 단계부터 마이크로칩 설계의 보안 수준을 테스트하는 효과적인 방법을 제시합니다.

하드웨어 보안 평가의 획기적인 솔루션

본 발명은 실제 칩 제조까지 기다리지 않고도 시뮬레이션을 통해 추정된 전력 소비 추적을 분석하여 설계 단계에서 암호화 하드웨어 설계의 보안을 평가할 수 있는 체계적인 기술 프로세스를 제공합니다.

전통적으로 하드웨어 보안 테스트는 설계가 ASIC이나 FPGA 칩으로 제작된 후에만 수행되어 비용과 시간이 많이 소요됩니다. 부채널 공격이 점점 더 정교해짐에 따라 정보 유출을 조기에 탐지하는 것이 시급해지고 있습니다.

특허받은 프로세스는 설계 명세, RTL 아키텍처 기술, 기능 시뮬레이션, 하드웨어 합성, 타이밍 및 기생 분석부터 T-검정, 미분 근사(DPA), 상관 분석(CPA)과 같은 통계 기법을 통한 전력 소비량 추정 및 보안 분석까지 다양한 단계를 포함합니다. 이 모든 프로세스는 제조 단계로 전송되기 전에 설계 모델에서 수행되므로 상당한 비용 절감과 악용 가능한 보안 취약점의 조기 탐지가 가능합니다.

고보안 마이크로 회로 설계의 실용적 응용

본 발명은 은행 카드, 전자 시민 식별, 군사 시스템, 보안 IoT 및 보안 임베디드 장치와 같이 높은 보안이 요구되는 애플리케이션을 제공하는 AES(고급 암호화 표준), RSA(공개 키 암호화), ECC(곡선 기반 암호화)와 같은 하드웨어 암호화 블록을 설계하고 평가하는 데 특히 유용합니다.

예를 들어, 하드웨어 설계가 제대로 보호되지 않으면 전력 로깅 공격으로 AES 키가 몇 분 안에 해독될 수 있습니다. 이 특허 솔루션은 설계 시 비밀 키 유출에 대한 내구성을 검증하고 향상시키는 강력한 기술 도구를 제공합니다.

이 솔루션에 대한 특허 부여는 반도체 설계 및 정보 보안 분야에서 베트남 과학자 들의 연구 개발 역량을 입증하는 것입니다. 이는 정부가 투자 및 개발을 우선시하는 첨단 기술 분야입니다.

이는 하드웨어 암호화, 사이드 채널 보안 분석, 디지털 회로 설계(RTL/ASIC/FPGA) 및 시제품 보안 설계 테스트와 같은 현재 주요 연구 방향의 효과적인 조합을 보여주는 사례이기도 합니다.

특허받은 기술 공정

전력 소비 추정 트레이스를 기반으로 한 하드웨어 보안 평가 프로세스는 다음 단계를 통해 수행됩니다. (i) 암호화/보안 설계 사양 개발; (ii) 레지스터 시프트(RTL) 형식의 하드웨어 설계; (iii) 설계 기능 시뮬레이션 및 검증; (iv) 설계 하드웨어 합성 및 구현; (v) 기생 임피던스 및 커패시턴스 정보 추출, 정적 타이밍 분석을 통해 설계의 타이밍 응답 확인; (vi) 기생 정보를 사용하여 설계 시뮬레이션 및 신호 파형 추출; (vii) 전력 소비 추정 및 해당 트레이스 추출; (viii) 전력 소비 트레이스 보간 및 추출; (ix) 수집된 트레이스를 기반으로 한 보안 평가; (x) IC 제조를 위해 설계를 시스템에 통합.

특허명: 전력 소비량 추정 추적 기반 하드웨어 보안 평가 프로세스

분야 : 반도체 설계, 하드웨어 보안

발급 기관: 과학기술부 지식재산부

응용 분야: 생산 전 ASIC/FPGA 기반 암호화 칩 설계의 보안 테스트

연구부서: 베트남 국립대학교 하노이 정보기술연구소 마이크로칩 설계 및 응용 연구 센터(CICA)

발명자: Bui Duy Hieu 박사, 교수, Tran Xuan Tu 박사

출처: https://nhandan.vn/buoc-tien-quan-trong-trong-nghien-cuu-thiet-ke-vi-mach-tai-viet-nam-post894360.html

![[사진] 제13기 당중앙위원회 제14차 대표자회 개막](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/05/1762310995216_a5-bnd-5742-5255-jpg.webp)

![[인포그래픽] 2030년까지 1학년부터 영어교육을 100% 실현하기 위해 노력](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/11/06/1762385718190_nhung-tiet-hoc-chuyen-doi-so-luon-soi-dong-hap-dan-hoc-sinh-1-7103-8710-jpg.webp)

![[사진] 2025-2030년 기간의 Nhan Dan 신문 애국모범대회 전경](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762252775462_ndo_br_dhthiduayeuncbaond-6125-jpg.webp)

댓글 (0)