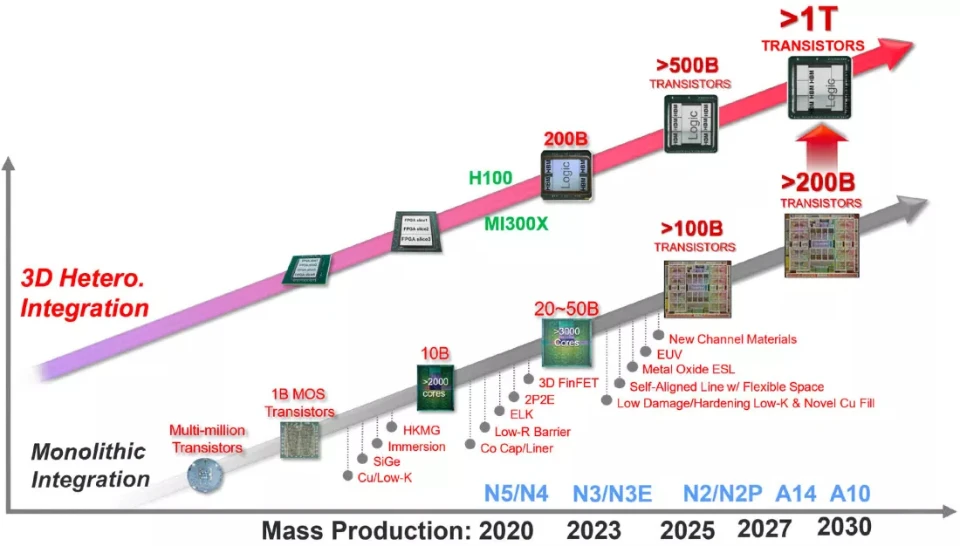

Techspotによると、TSMCは先日開催されたIEDMカンファレンスにおいて、次世代半導体製造プロセスの製品ロードマップを発表しました。このロードマップでは、最終的には1つのチップパッケージに1兆個のトランジスタを搭載した複数の3D積層チップレット設計を提供する予定です。CoWoS、InFO、SoICといったパッケージング技術の進歩により、同社はこの目標を達成できると見ており、2030年までにモノリシック設計で2,000億個のトランジスタを実現できるとTSMCは考えています。

TSMCは2030年までに1nmチップを製造できると考えている

NVIDIAの800億トランジスタ搭載のGH100は、市場で最も複雑なモノリシックチップの一つです。しかし、これらのチップが大型化し、価格も高騰するにつれて、メーカーはAMDが最近発売したInstinct MI300XやIntelの1000億トランジスタ搭載のPonte Vecchioのようなマルチチップレットアーキテクチャを採用するようになるだろうとTSMCは考えています。

TSMCは今のところ、2nm N2およびN2P製造プロセスに加え、1.4nm A14および1nm A10チップの開発を継続します。同社は2025年末までに2nmプロセスでの生産を開始する予定です。2028年には1.4nm A14プロセスに移行し、2030年までに1nmトランジスタの生産を開始する予定です。

一方、Intelは2nm(20A)および1.8nm(18A)プロセスの開発に取り組んでおり、同時期に発売される予定です。この新技術の利点の一つは、ロジック密度の向上、クロック速度の向上、リーク電流の低減を実現し、よりエネルギー効率の高い設計につながることです。

TSMCの次世代先進チップ開発の目標

世界最大のファウンドリーであるTSMCは、自社の製造プロセスがインテルのどの製品よりも優れていると確信しています。TSMCのCEOであるCC Wei氏は、決算説明会で、社内レビューによりN3P技術の改良が確認され、同社の3nm製造プロセスはインテルの18Aプロセスと「PPA(製造原価)で同等」であることが証明されたと述べました。彼は、N3Pがさらに優れた技術となり、競争力を高め、大幅なコスト優位性を持つと期待しています。

一方、インテルのCEO、パット・ゲルシンガー氏は、自社の18A製造プロセスが、1年前にリリースされたTSMCの2nmチップよりも優れた性能を発揮すると主張している。もちろん、真相は時が経てば分かるだろう。

[広告2]

ソースリンク

![[写真] ホーチミン市の若者がよりきれいな環境を求めて行動を起こす](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762233574890_550816358-1108586934787014-6430522970717297480-n-1-jpg.webp)

![[写真] 2025年から2030年までのニャンダン新聞愛国模範大会のパノラマ](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762252775462_ndo_br_dhthiduayeuncbaond-6125-jpg.webp)

コメント (0)