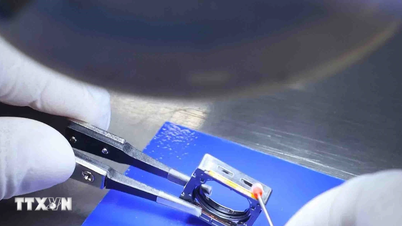

ຊອບແວການປັບປຸງນີ້ເພີ່ມຄຸນສົມບັດຈໍາລອງສໍາລັບມາດຕະຖານ Universal Chiplet Interconnect Express (UCIe) 2.0 ແລະເພີ່ມການສະຫນັບສະຫນູນສໍາລັບມາດຕະຖານ Bunch of Wires (BoW) ຂອງໂຄງການຄອມພິວເຕີເປີດ. ໃນຖານະທີ່ເປັນການແກ້ໄຂແບບຕາຍເພື່ອຕາຍ (D2D) ແລະລະດັບລະບົບ chiplet, Chiplet PHY Designer ຊ່ວຍໃຫ້ການກວດສອບລະດັບຊິລິໂຄນກ່ອນ, ເຮັດໃຫ້ການອອກແບບຊິບ ແລະຂະບວນການຜະລິດງ່າຍຂຶ້ນ.

ເທັກໂນໂລຍີ Keysight ໃນປັດຈຸບັນສະຫນັບສະຫນູນການແກ້ໄຂການປຸງແຕ່ງຂໍ້ມູນຕ່າງໆ

ເນື່ອງຈາກ AI ແລະຊິບສູນຂໍ້ມູນກາຍເປັນຄວາມສັບສົນຫຼາຍຂື້ນ, ການຮັບປະກັນການສື່ສານທີ່ເຊື່ອຖືໄດ້ລະຫວ່າງຊິບແມ່ນສໍາຄັນຕໍ່ການປະຕິບັດ. ຕະຫຼາດກໍາລັງແກ້ໄຂສິ່ງທ້າທາຍນີ້ກັບມາດຕະຖານເປີດທີ່ພົ້ນເດັ່ນຂື້ນເຊັ່ນ UCIe ແລະ BoW ເພື່ອກໍານົດການເຊື່ອມຕໍ່ລະຫວ່າງຊິບໃນ 2.5D ປັບປຸງ / 3D ຫຼືການຫຸ້ມຫໍ່ / ປັບປຸງ. ໂດຍການຮັບຮອງເອົາມາດຕະຖານເຫຼົ່ານີ້ແລະການກວດສອບການປະຕິບັດຕາມ chiplet, ຜູ້ອອກແບບປະກອບສ່ວນເຂົ້າໃນການພັດທະນາລະບົບນິເວດຂອງ chiplet interoperability, ການຫຼຸດຜ່ອນຄ່າໃຊ້ຈ່າຍແລະຄວາມສ່ຽງຂອງການພັດທະນາເຕັກໂນໂລຊີ semiconductor.

ການແກ້ໄຂຍັງຊ່ວຍຫຼຸດເວລາໃນການຕະຫຼາດ, ອັດຕະໂນມັດການຈໍາລອງແລະການຕິດຕັ້ງການທົດສອບການປະຕິບັດຕາມ, ເຊັ່ນ: ຟັງຊັນການຖ່າຍທອດແຮງດັນ (VTF), ແລະເຮັດໃຫ້ຂະບວນການອອກແບບ chiplet ງ່າຍດາຍ.

"ຫນຶ່ງປີກ່ອນ, Keysight EDA ໄດ້ເປີດຕົວ Chiplet PHY Designer ເປັນເຄື່ອງມືກວດສອບທາງສ່ວນຫນ້າຂອງຊິລິໂຄນທໍາອິດຂອງຕະຫຼາດທີ່ມີການສ້າງແບບຈໍາລອງແລະຄວາມສາມາດໃນການຈໍາລອງໃນຄວາມເລິກ; ມັນຊ່ວຍໃຫ້ນັກອອກແບບ chiplet ສາມາດກວດສອບໄດ້ໄວແລະຖືກຕ້ອງວ່າການອອກແບບຂອງພວກເຂົາຕອບສະຫນອງສະເພາະກ່ອນການຜະລິດ," Hee-Soo Lee, ຫົວຫນ້າການພັດທະນາລູກຄ້າ, ຄວາມໄວສູງ, Keysight EDA ກ່າວ. "ການປ່ອຍຫລ້າສຸດຕອບສະຫນອງມາດຕະຖານການພັດທະນາເຊັ່ນ UCIe 2.0 ແລະ BoW, ແລະສະຫນອງຄຸນນະສົມບັດໃຫມ່ເຊັ່ນ: ແຜນທີ່ໂມງ QDR ແລະການວິເຄາະລະບົບ crosstalk ສໍາລັບລົດເມ unidirectional. ວິສະວະກອນໃຊ້ Chiplet PHY Designer ເພື່ອປະຫຍັດເວລາແລະຫຼຸດຜ່ອນຄວາມຜິດພາດ, ຮັບປະກັນການອອກແບບຂອງພວກເຂົາຕອບສະຫນອງຄວາມຕ້ອງການດ້ານການປະຕິບັດກ່ອນການຜະລິດ."

ທີ່ມາ: https://thanhnien.vn/keysight-ra-mat-giai-phap-thiet-ke-chiplet-ky-thuat-so-toc-do-cao-moi-185250205141620491.htm

![ການຫັນປ່ຽນ OCOP ດົງນາຍ: [ມາດຕາ 3] ເຊື່ອມໂຍງການທ່ອງທ່ຽວກັບການບໍລິໂພກຜະລິດຕະພັນ OCOP](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/11/10/1762739199309_1324-2740-7_n-162543_981.jpeg)

(0)