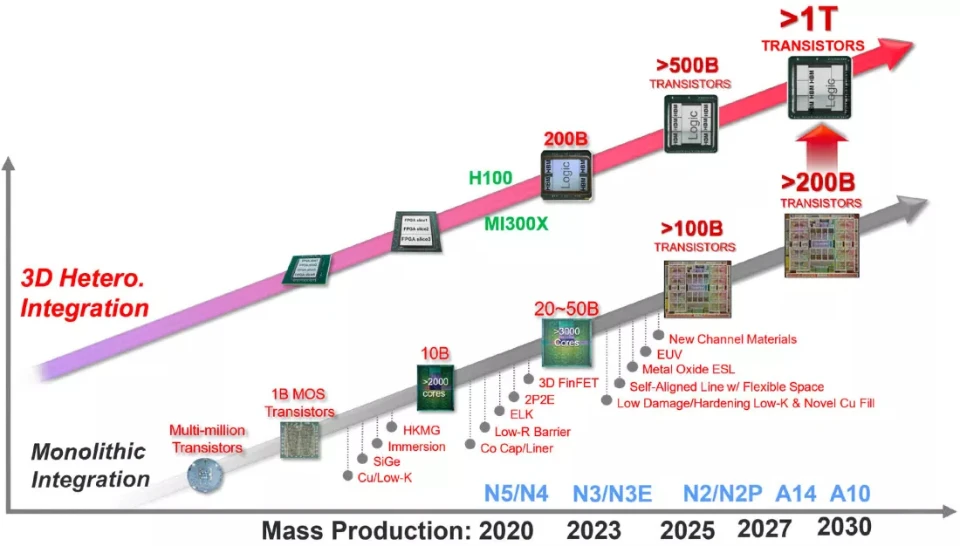

לפי Techspot , בכנס IEDM האחרון, הכריזה TSMC על מפת דרכים למוצרים לתהליכי ייצור מוליכים למחצה מהדור הבא שלה, שהגיעה לשיאה בהצעת קולקציה של עיצובי שבבים תלת-ממדיים עם טריליון טרנזיסטורים לכל חבילת שבב בודדת. התקדמות בטכנולוגיית האריזות, כגון CoWoS, InFO ו-SoIC, תאפשר לחברה להשיג מטרה זו, ועד שנת 2030, TSMC מאמינה שעיצוביה המונוליטיים יוכלו להגיע ל-200 מיליארד טרנזיסטורים.

TSMC מאמינה שהיא תוכל לייצר שבבים במהירות של 1 ננומטר עד 2030.

ה-GH100 של Nvidia, עם 80 מיליארד טרנזיסטורים שלו, הוא אחד השבבים המונוליטיים המורכבים ביותר הקיימים כיום בשוק. עם זאת, ככל שגודל השבבים הללו ימשיך לגדול והם יהפכו יקרים יותר, TSMC מאמינה כי יצרנים יאמצו ארכיטקטורות מרובות שבבים, כמו ה-Instinct MI300X שהשיקה לאחרונה של AMD וה-Ponte Vecchio של אינטל, הכוללים 100 מיליארד טרנזיסטורים.

נכון לעכשיו, TSMC תמשיך לפתח תהליכי ייצור של N2 ו-N2P ב-2 ננומטר, כמו גם את שבבי A14 ב-1.4 ננומטר ו-A10 ב-1 ננומטר. החברה צופה להתחיל בייצור ב-2 ננומטר עד סוף 2025. בשנת 2028 היא תעבור לתהליך A14 ב-1.4 ננומטר, ועד 2030 היא צפויה לייצר טרנזיסטורים ב-1 ננומטר.

בינתיים, אינטל עובדת על תהליכים של 2 ננומטר (20A) ו-1.8 ננומטר (18A), שצפויים להיות מושקים באותו פרק זמן. יתרון אחד של הטכנולוגיה החדשה הוא שהיא מציעה צפיפות לוגית גבוהה יותר, מהירויות שעון מוגברות ודליפת חשמל נמוכה יותר, וכתוצאה מכך עיצובים חסכוניים יותר באנרגיה.

מטרותיה של TSMC לפיתוח הדור הבא של שבבים מתקדמים.

כבית היציקה הגדול בעולם , TSMC בטוחה שתהליכי הייצור שלה יעלו על כל מוצר של אינטל. בשיחת ועידה בנושא דיווחים פיננסיים, הצהיר מנכ"ל TSMC, סי.סי. ווי, כי הערכות פנימיות אישרו את השיפורים בטכנולוגיית N3P ובתהליך הייצור של החברה ב-3 ננומטר, מה שמוכיח ש-"PPA" שלה דומה" לתהליך 18A של אינטל. הוא מצפה ש-N3P יהיה אפילו טוב יותר, תחרותי יותר, ויציע יתרונות משמעותיים מבחינת עלות.

בינתיים, מנכ"ל אינטל, פאט גלסינגר, טען שתהליך הייצור של שבבי ה-18A שלהם יעלה על שבבי ה-2nm של TSMC שהושקו שנה קודם לכן. כמובן, רק הזמן יגיד.

[מודעה_2]

קישור למקור

![[תמונה] ראש הממשלה פאם מין צ'ין מקבל את פני מושל מחוז טוצ'יגי (יפן)](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F16%2F1765892133176_dsc-8082-6425-jpg.webp&w=3840&q=75)

![[תמונה] ראש הממשלה פאם מין צ'ין מקבל את פניה של שרת החינוך והספורט של לאוס, תונגסלית מנגנורק](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F16%2F1765876834721_dsc-7519-jpg.webp&w=3840&q=75)

![[תמונה] תמונות שדלפו לקראת טקס פרסי הפעולה הקהילתית 2025.](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F16%2F1765882828720_ndo_br_thiet-ke-chua-co-ten-45-png.webp&w=3840&q=75)

![[חי] טקס פרסי פעולה קהילתית 2025](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F16%2F1765899631650_ndo_tr_z7334013144784-9f9fe10a6d63584c85aff40f2957c250-jpg.webp&w=3840&q=75)

![[שידור חי] טקס סיום וחלוקת פרסים לתחרות יצירת וידאו/קליפים "תיירות מרשימה בווייטנאם" 2025](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/12/17/1765974650260_z7273498850699-00d2fd6b0972cb39494cfa2559bf85ac-1765959338756946072104-627-0-1338-1138-crop-1765959347256801551121.jpeg)

תגובה (0)