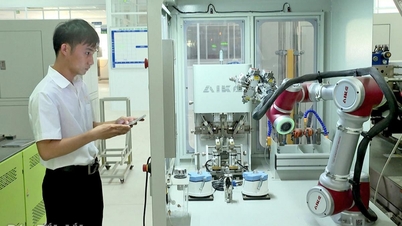

នេះគឺជាលទ្ធផលនៃការស្រាវជ្រាវដោយក្រុមស្រាវជ្រាវប្រព័ន្ធរួមបញ្ចូលគ្នាឆ្លាតវៃ (SISLAB) - មជ្ឈមណ្ឌលស្រាវជ្រាវ និងប្រើប្រាស់មីក្រូឈីប វិទ្យាស្ថានបច្ចេកវិទ្យាព័ត៌មាន សាកលវិទ្យាល័យជាតិវៀតណាម ទីក្រុងហាណូយ។ ការងារនេះបើកនូវវិធីសាស្រ្តដ៏មានប្រសិទ្ធភាពមួយក្នុងការសាកល្បងកម្រិតសុវត្ថិភាពនៃការរចនាមីក្រូឈីបភ្លាមៗពីដំណាក់កាលរចនា មុនពេលផលិត។

ដំណោះស្រាយបំបែកនៅក្នុងការវាយតម្លៃសុវត្ថិភាពផ្នែករឹង

ការបង្កើតថ្មីនេះផ្តល់នូវដំណើរការបច្ចេកទេសជាប្រព័ន្ធដែលអនុញ្ញាតឱ្យវាយតម្លៃសុវត្ថិភាពនៃការរចនាផ្នែករឹងគ្រីបតូ ក្នុងអំឡុងពេលនៃការរចនា តាមរយៈការវិភាគនៃដានការប្រើប្រាស់ថាមពលដែលបានប៉ាន់ស្មានដោយការក្លែងធ្វើ ជំនួសឱ្យការរង់ចាំរហូតដល់ការផលិតបន្ទះឈីបពិតប្រាកដ។

ជាប្រពៃណី ការធ្វើតេស្តសុវត្ថិភាពផ្នែករឹងត្រូវបានអនុវត្តតែបន្ទាប់ពីការរចនាត្រូវបានប្រឌិតចូលទៅក្នុងបន្ទះឈីប ASIC ឬ FPGA ដែលមានតម្លៃថ្លៃ និងចំណាយពេលច្រើន។ ជាមួយនឹងការវាយប្រហារតាមឆានែលចំហៀងកាន់តែមានភាពស្មុគ្រស្មាញ ការរកឃើញមុននៃការលេចធ្លាយព័ត៌មានកំពុងក្លាយជារឿងបន្ទាន់។

ដំណើរការដែលមានប៉ាតង់រួមមានជំហានពីការបញ្ជាក់ការរចនា ការពិពណ៌នាអំពីស្ថាបត្យកម្ម RTL ការក្លែងធ្វើមុខងារ ការសំយោគផ្នែករឹង ការកំណត់ពេល និងការវិភាគប៉ារ៉ាស៊ីត ដល់ការប៉ាន់ប្រមាណការប្រើប្រាស់ថាមពល និងការវិភាគសុវត្ថិភាពតាមរយៈបច្ចេកទេសស្ថិតិដូចជា T-test ការប៉ាន់ស្មានឌីផេរ៉ង់ស្យែល (DPA) និងការវិភាគទំនាក់ទំនង (CPA)។ ដំណើរការទាំងមូលត្រូវបានអនុវត្តលើគំរូរចនា មុនពេលបញ្ជូនវាទៅការផលិត ដែលបណ្តាលឱ្យមានការសន្សំថ្លៃដើមដ៏សំខាន់ និងការរកឃើញដំបូងនៃភាពងាយរងគ្រោះសុវត្ថិភាពដែលអាចកេងប្រវ័ញ្ចបាន។

កម្មវិធីជាក់ស្តែងក្នុងការរចនានៃ microcircuits សុវត្ថិភាពខ្ពស់។

ការច្នៃប្រឌិតនេះមានប្រយោជន៍ជាពិសេសក្នុងការរចនា និងវាយតម្លៃប្លុកការអ៊ិនគ្រីបផ្នែករឹងដូចជា AES (ស្តង់ដារការអ៊ិនគ្រីបកម្រិតខ្ពស់), RSA (ការគ្រីបសោសាធារណៈ), ECC (ការគ្រីបដែលមានមូលដ្ឋានលើខ្សែកោង)... បម្រើកម្មវិធីដែលទាមទារសុវត្ថិភាពខ្ពស់ដូចជាកាតធនាគារ អត្តសញ្ញាណពលរដ្ឋអេឡិចត្រូនិក ប្រព័ន្ធ យោធា សុវត្ថិភាព IoT និងឧបករណ៍បង្កប់សុវត្ថិភាព។

ឧទាហរណ៍ ការវាយប្រហារដោយថាមពលអាចបំបែកសោ AES ក្នុងរយៈពេលប៉ុន្មាននាទី ប្រសិនបើការរចនាផ្នែករឹងមិនត្រូវបានការពារត្រឹមត្រូវ។ ដំណោះស្រាយដែលមានប៉ាតង់នេះផ្តល់នូវឧបករណ៍បច្ចេកទេសដ៏មានឥទ្ធិពលមួយដើម្បីផ្ទៀងផ្ទាត់ និងកែលម្អភាពធន់នៃការលេចធ្លាយគន្លឹះសម្ងាត់នៅក្នុងការរចនា។

ការផ្តល់ប័ណ្ណប៉ាតង់សម្រាប់ដំណោះស្រាយនេះ បញ្ជាក់ពីសមត្ថភាពស្រាវជ្រាវ និងអភិវឌ្ឍន៍របស់ អ្នកវិទ្យាសាស្ត្រ វៀតណាមក្នុងវិស័យរចនា semiconductor និងសន្តិសុខព័ត៌មាន ដែលជាវិស័យបច្ចេកវិទ្យាខ្ពស់ដែលកំពុងត្រូវបានផ្តល់អាទិភាពសម្រាប់ការវិនិយោគ និងអភិវឌ្ឍន៍ដោយរដ្ឋាភិបាល។

នេះក៏ជាការបង្ហាញអំពីការរួមបញ្ចូលគ្នាដ៏មានប្រសិទ្ធភាពនៃទិសដៅស្រាវជ្រាវសំខាន់ៗនាពេលបច្ចុប្បន្ន ដូចជាការគ្រីបផ្នែករឹង ការវិភាគសុវត្ថិភាពឆានែលចំហៀង ការរចនាសៀគ្វីឌីជីថល (RTL/ASIC/FPGA) និងការធ្វើតេស្តការរចនាសុវត្ថិភាពមុនផលិតកម្ម។

ដំណើរការបច្ចេកទេសដែលមានប៉ាតង់

ដំណើរការនៃការវាយតម្លៃសុវត្ថិភាពផ្នែករឹងដោយផ្អែកលើដាននៃការប៉ាន់ប្រមាណការប្រើប្រាស់ថាមពលត្រូវបានអនុវត្តតាមជំហានដូចខាងក្រោមៈ (i) ការបង្កើតលក្ខណៈបច្ចេកទេសនៃការរចនាកូដសម្ងាត់/សុវត្ថិភាព។ (ii) ការរចនាផ្នែករឹងក្នុងទម្រង់ register-shift (RTL); (iii) ការក្លែងធ្វើ និងផ្ទៀងផ្ទាត់មុខងារនៃការរចនា។ (iv) ការសំយោគ និងការអនុវត្តផ្នែករឹងនៃការរចនា។ (v) ទាញយកព័ត៌មានអំពីឧបសគ្គប៉ារ៉ាស៊ីត និងសមត្ថភាព វិភាគពេលវេលាឋិតិវន្ត ដើម្បីពិនិត្យមើលការឆ្លើយតបពេលវេលារបស់ការរចនា។ (vi) ក្លែងធ្វើការរចនាជាមួយនឹងព័ត៌មានប៉ារ៉ាស៊ីត និងការទាញយកទម្រង់រលកសញ្ញា។ (vii) ការប៉ាន់ប្រមាណការប្រើប្រាស់ថាមពល និងការទាញយកដានដែលត្រូវគ្នា; (viii) ការជ្រៀតជ្រែក និងការទាញយកដាននៃការប្រើប្រាស់ថាមពល។ (ix) ការវាយតម្លៃសុវត្ថិភាពដោយផ្អែកលើដានដែលប្រមូលបាន; (x) ការរួមបញ្ចូលការរចនាទៅក្នុងប្រព័ន្ធ ត្រៀមខ្លួនសម្រាប់ការផលិត IC ។

ចំណងជើងប៉ាតង់៖ ដំណើរការវាយតម្លៃសុវត្ថិភាពផ្នែករឹងដោយផ្អែកលើដាននៃការប៉ាន់ប្រមាណការប្រើប្រាស់ថាមពល

វាល: ការរចនា semiconductor, សុវត្ថិភាពផ្នែករឹង

សិទ្ធិអំណាច៖ នាយកដ្ឋានកម្មសិទ្ធិបញ្ញា - ក្រសួងវិទ្យាសាស្ត្រ និងបច្ចេកវិទ្យា

កម្មវិធី៖ ការធ្វើតេស្តសុវត្ថិភាពនៃការរចនាបន្ទះឈីបគ្រីបគ្រីបដែលមានមូលដ្ឋានលើ ASIC/FPGA មុនពេលផលិត

អង្គភាពស្រាវជ្រាវ៖ មជ្ឈមណ្ឌលស្រាវជ្រាវ និងប្រើប្រាស់មីក្រូឈីប (CICA) វិទ្យាស្ថានបច្ចេកវិទ្យាព័ត៌មាន សាកលវិទ្យាល័យជាតិវៀតណាម ទីក្រុងហាណូយ

អ្នកបង្កើត៖ បណ្ឌិត Bui Duy Hieu សាស្ត្រាចារ្យបណ្ឌិត Tran Xuan Tu

ប្រភព៖ https://nhandan.vn/buoc-tien-quan-trong-trong-nghien-cuu-thiet-ke-vi-mach-tai-viet-nam-post894360.html

![[រូបថត] បើកសន្និសីទលើកទី១៤ នៃគណៈកម្មាធិការមជ្ឈិមបក្សលើកទី១៣](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/05/1762310995216_a5-bnd-5742-5255-jpg.webp)

![[Infographic] ខិតខំឱ្យសាលាបង្រៀនភាសាអង់គ្លេសចាប់ពីថ្នាក់ទី ១ ដល់ឆ្នាំ ២០៣០ ១០០%](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/11/06/1762385718190_nhung-tiet-hoc-chuyen-doi-so-luon-soi-dong-hap-dan-hoc-sinh-1-7103-8710-jpg.webp)

![[រូបថត] ទិដ្ឋភាពនៃសមាជត្រាប់តាមស្នេហាជាតិនៃកាសែត Nhan Dan សម្រាប់រយៈពេល 2025-2030](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762252775462_ndo_br_dhthiduayeuncbaond-6125-jpg.webp)

Kommentar (0)