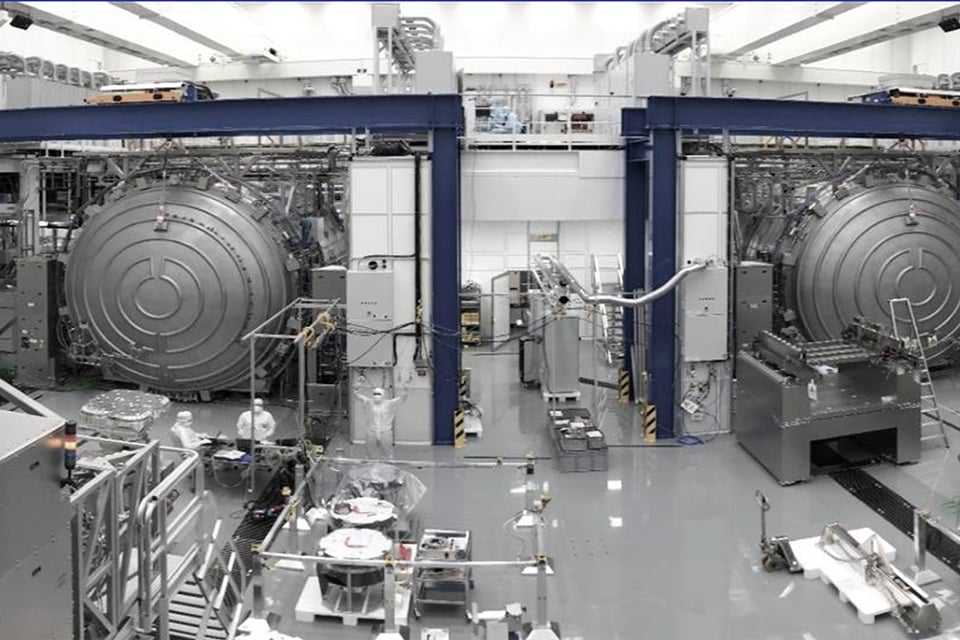

PhoneArena 에 따르면 TSMC와 삼성 파운드리는 2025년에 2nm 칩 양산을 시작할 것으로 예상되며, 이는 인텔이 1.8nm 칩을 통해 칩 제조 공정을 주도할 수 있음을 의미합니다. 인텔은 EUV 고개방형(High-NA) 장비 한 대당 3억 달러에서 4억 달러를 투자할 것으로 알려졌습니다.

ASML High-NA 기계 한 대의 가격은 최소 3억 달러입니다.

ASML은 이번 인도에 대해 "최초의 High-NA 시스템을 출하하고 있으며, 소셜 미디어 게시물을 통해 이를 발표했습니다. 이 시스템은 이전에 발표된 대로 계획대로 인텔에 인도될 것입니다."라고 밝혔습니다.

고개구수(High-NA) 시스템에서는 개구수가 높을수록 실리콘 웨이퍼에 식각되는 패턴의 해상도가 높아집니다. 기존 EUV 장비의 개구수는 0.33(13nm 해상도에 해당)인 반면, 고개구수 장비는 개구수가 0.55(8nm 해상도에 해당)입니다. 고해상도 패턴이 웨이퍼에 전사되면 파운드리에서 추가 기능을 추가하기 위해 웨이퍼를 EUV 장비에 두 번 통과시킬 필요가 없어 시간과 비용을 절약할 수 있습니다.

고개수 EUV 장비는 주로 트랜지스터 크기를 줄이고 집적도를 높여 칩 내부에 더 많은 트랜지스터를 집적하는 데 중점을 둡니다. 칩에 트랜지스터가 많을수록 칩의 성능과 에너지 효율이 향상됩니다. 고개수 EUV 장비를 사용하면 트랜지스터 크기를 1.7배 줄이는 동시에 집적도를 2.9배 높일 수 있습니다.

각 High-NA 기계는 ASML에서 13개의 대형 컨테이너로 배송됩니다.

새로운 버전의 고개수 EUV 머신은 2nm 이하 칩 생산을 가능하게 할 것입니다. 바로 지난주, TSMC와 삼성 파운드리는 2nm 이후 로드맵을 발표했습니다. 두 회사는 2027년까지 1.4nm 공정을 사용하여 반도체를 개발할 계획입니다. 2nm 칩 생산은 2025년에 시작될 것으로 예상되며, 며칠 전 TSMC는 애플이 2nm 칩 프로토타입을 평가할 수 있도록 허용했습니다.

EUV 고개수(High-NA) 장비를 운반하는 것은 13개의 대형 컨테이너와 250개의 상자로 나뉘어져 있어 쉬운 작업이 아니었습니다. 장비 조립 또한 매우 어려웠습니다.

[광고_2]

소스 링크

![[사진] 산사태로 피해를 입은 14E 도로에서 사람들이 통행할 수 있도록 언덕을 깎아내는 모습](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/08/1762599969318_ndo_br_thiet-ke-chua-co-ten-2025-11-08t154639923-png.webp)

![[영상] 후에 기념물 재개장, 방문객 맞이](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/11/05/1762301089171_dung01-05-43-09still013-jpg.webp)

댓글 (0)