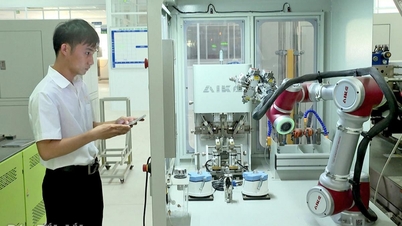

これは、ハノイにあるベトナム国家大学情報技術研究所マイクロチップ設計・応用研究センターのインテリジェント統合システム研究グループ(SISLAB)による研究成果です。この研究は、生産前の設計段階からマイクロチップ設計のセキュリティレベルをテストするための効果的なアプローチを開拓します。

ハードウェアセキュリティ評価における画期的なソリューション

本発明は、実際のチップ製造まで待つことなく、設計段階でシミュレーションによって推定された電力消費トレースの分析を通じて暗号ハードウェア設計のセキュリティを評価できる体系的な技術プロセスを提供する。

従来、ハードウェアセキュリティテストは、設計がASICまたはFPGAチップに製造された後にのみ実施されており、コストと時間がかかります。サイドチャネル攻撃がますます巧妙化しているため、情報漏洩の早期検出が急務となっています。

特許取得済みのプロセスには、設計仕様、RTLアーキテクチャ記述、機能シミュレーション、ハードウェア合成、タイミングおよび寄生解析から、T検定、差分近似法(DPA)、相関分析(CPA)などの統計手法による消費電力推定およびセキュリティ解析まで、一連のステップが含まれます。このプロセス全体は、製造工程に送る前に設計モデル上で実行されるため、大幅なコスト削減と、悪用可能なセキュリティ脆弱性の早期検出につながります。

高セキュリティマイクロ回路の設計における実用化

本発明は、銀行カード、電子国民識別、軍事システム、セキュア IoT、セキュア組み込みデバイスなど、高度なセキュリティを必要とするアプリケーションに対応する、AES (高度暗号化規格)、RSA (公開鍵暗号化)、ECC (曲線ベース暗号化) などのハードウェア暗号化ブロックの設計と評価に特に役立ちます。

例えば、ハードウェア設計が適切に保護されていない場合、電力ロギング攻撃によってAES鍵が数分で解読される可能性があります。この特許取得済みソリューションは、設計における秘密鍵漏洩に対する耐性を検証し、向上させるための強力な技術ツールを提供します。

このソリューションに対する特許の付与は、政府が投資と開発の優先分野としているハイテク分野である半導体設計と情報セキュリティの分野におけるベトナムの科学者の研究開発能力を証明するものです。

これは、ハードウェア暗号化、サイドチャネルセキュリティ分析、デジタル回路設計 (RTL/ASIC/FPGA)、生産前セキュリティ設計テストなど、現在の主要な研究方向の効果的な組み合わせを示すものでもあります。

特許取得済みの技術プロセス

消費電力推定トレースを基にしたハードウェア セキュリティ評価のプロセスは、以下の手順で実行されます: (i) 暗号化/セキュリティ設計仕様の開発、(ii) レジスタ シフト (RTL) 形式でのハードウェア設計、(iii) 設計機能のシミュレーションと検証、(iv) 設計ハードウェアの合成と実装、(v) 寄生インピーダンスおよび容量情報の抽出、静的タイミングの解析による設計のタイミング応答の確認、(vi) 寄生情報を使用した設計のシミュレーションと信号波形の抽出、(vii) 消費電力の推定と対応するトレースの抽出、(viii) 消費電力トレースの補間と抽出、(ix) 収集されたトレースを基にしたセキュリティ評価、(x) IC 製造の準備として設計をシステムに統合。

特許名称: 消費電力推定トレースに基づくハードウェアセキュリティ評価プロセス

分野: 半導体設計、ハードウェアセキュリティ

発行機関:科学技術省知的財産局

用途: 生産前のASIC/FPGAベースの暗号化チップ設計のセキュリティテスト

研究ユニット:ベトナム国家大学情報技術研究所マイクロチップ設計・応用研究センター(CICA)、ハノイ

発明者: ブイ・デュイ・ヒエウ博士、教授、トラン・スアン・トゥ博士

出典: https://nhandan.vn/buoc-tien-quan-trong-trong-nghien-cuu-thiet-ke-vi-mach-tai-viet-nam-post894360.html

![[インフォグラフィック] 2030年までに1年生から英語を教える学校の100%を目指す](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/11/06/1762385718190_nhung-tiet-hoc-chuyen-doi-so-luon-soi-dong-hap-dan-hoc-sinh-1-7103-8710-jpg.webp)

![[写真] 2025年から2030年までのニャンダン新聞愛国模範大会のパノラマ](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/04/1762252775462_ndo_br_dhthiduayeuncbaond-6125-jpg.webp)

コメント (0)