Jest to symboliczna inicjatywa mająca na celu promowanie współpracy między Japonią a Koreą Południową w tej branży.

Koszt budowy nowego obiektu wyniesie ponad 30 miliardów jenów (222 miliony dolarów amerykańskich). Obiekt powstanie w Jokohamie, na południowy zachód od Tokio, gdzie obecnie mieści się również siedziba Samsung Research and Development Institute Japan.

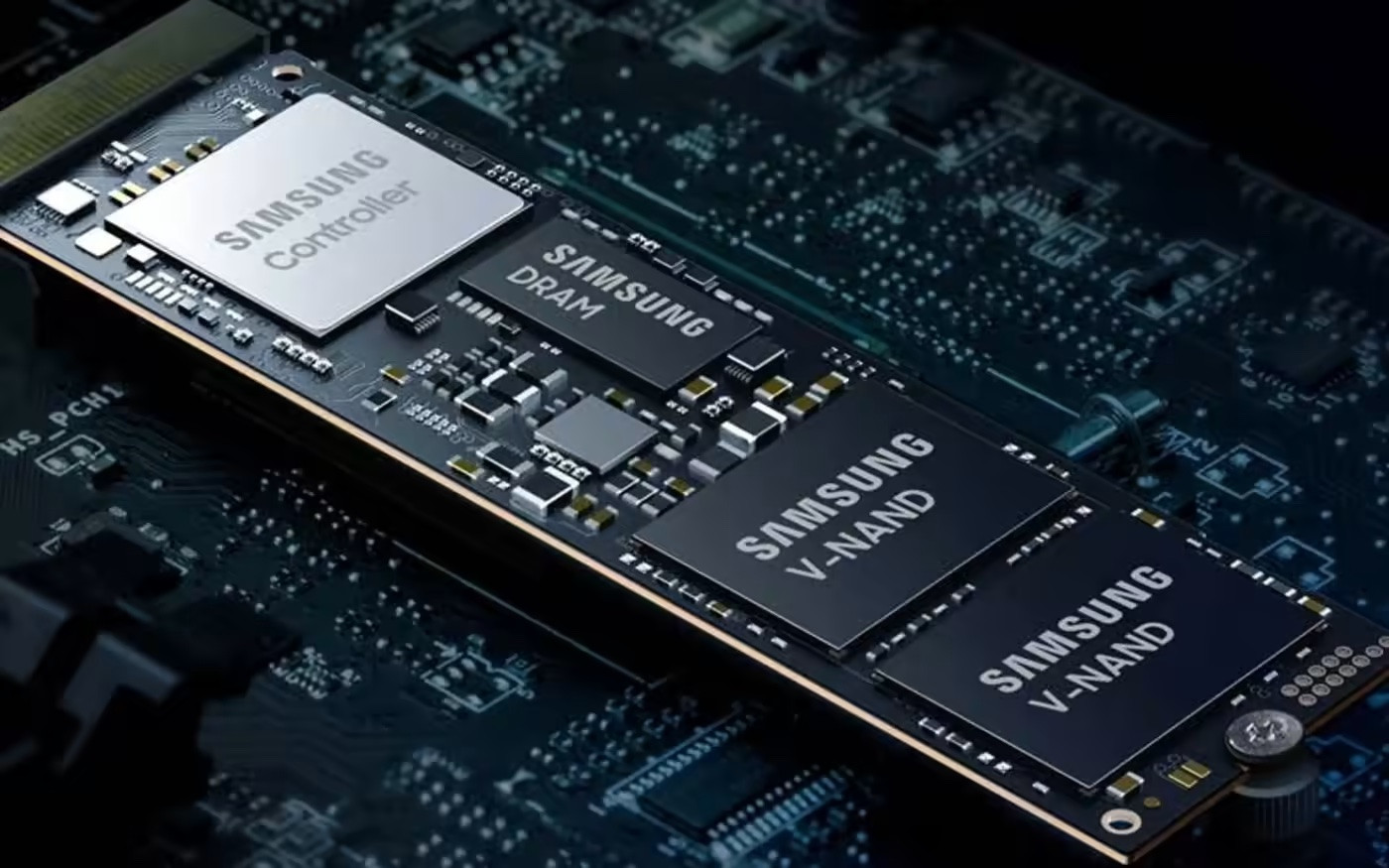

Samsung jest największym na świecie producentem układów pamięci, natomiast Japonia jest wiodącym producentem podstawowych materiałów do produkcji półprzewodników, takich jak płytki półprzewodnikowe i urządzenia odlewnicze.

Nowy zakład ma być gotowy do użytku do 2025 roku. Samsung zamierza skorzystać z dotacji od japońskiego rządu na łączną kwotę ponad 10 miliardów jenów dla sektora półprzewodników.

Działanie najcenniejszej firmy Korei Południowej może pobudzić współpracę między przemysłem półprzewodników w obu krajach.

Inwestycja jest konsekwencją nowego partnerstwa między Seulem a Tokio, na czele którego stoją prezydent Korei Południowej Yoon Suk Yeol i premier Japonii Fumio Kishida, którzy mają się spotkać przy okazji szczytu G7 w Hiroszimie w przyszłym tygodniu.

Główny rywal Samsunga, TSMC, również dokonał znaczącej inwestycji w Japonii w 2021 roku, dywersyfikując swoją bazę produkcyjną w obliczu obaw o nadmierną koncentrację produkcji chipów na Tajwanie. TSMC utrzymuje również ośrodek badawczo-rozwojowy w Tsukubie, na północny wschód od Tokio.

Japonia, niegdyś światowy lider w produkcji układów pamięci, stara się odbudować swoją bazę produkcyjną, przyciągając inwestycje zagraniczne. TSMC i Micron Technology to główni inwestorzy zagraniczni w Japonii, którzy otrzymali dotacje rządowe.

Nowy zakład Samsunga będzie zajmował się końcową częścią procesu produkcji półprzewodników, w szczególności pakowaniem płytek półprzewodnikowych zintegrowanych z płytkami drukowanymi w produkty finalne.

Tradycyjnie prace badawczo-rozwojowe koncentrowały się na wczesnych etapach procesu produkcyjnego, dążąc do maksymalnego zmniejszenia obwodów. Wielu uważa jednak, że dalsza miniaturyzacja ma swoje granice, a nacisk zostanie przesunięty na udoskonalenie procesów back-end, takich jak układanie płytek półprzewodnikowych w wielowarstwowe układy scalone w celu tworzenia układów scalonych 3D.

(Według NikkeiAsia)

Źródło

![[Zdjęcie] Sekretarz generalny To Lam i przewodniczący Zgromadzenia Narodowego Tran Thanh Man biorą udział w obchodach 80. rocznicy Tradycyjnego Dnia Wietnamskiego Sektora Inspekcyjnego](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/17/1763356362984_a2-bnd-7940-3561-jpg.webp)

Komentarz (0)