Det sista steget i chipdesignprocessen, känt som kiseluttag, är rigoröst, dyrt och lämnar lite utrymme för designfel. Om en design misslyckas efter uttag måste chiptillverkare starta en ny "omsnurrningscykel" som kan vara 12 månader eller mer. Förseningen som orsakas av denna omdesign kräver inte bara ytterligare, dyra forsknings- och utvecklingsresurser, utan kan också hindra chiptillverkare från att få ut sina produkter på marknaden i tid.

Keysight Technologies erbjuder ett brett utbud av mät- och testlösningar.

Keysights USPA-plattform ger chipdesigners och ingenjörer en digital tvilling av kompletta signaler för att verifiera design innan de går vidare till chiptillverkning, vilket minimerar risken för designfel och omdesignkostnader. USPA-plattformen integrerar ultrasnabba signalomvandlare med ett högpresterande FPGA-prototypsystem, vilket ger konstruktörer ett alternativ till proprietära, kundanpassade prototypsystem.

Dessutom tillhandahåller lösningen även lämpliga in-/utdatagränssnitt för applikationer inklusive utveckling av 6G-radioapplikationer, digitalt radiofrekvensminne, avancerad fysikforskning och höghastighetsdatainsamlingsapplikationer, såsom radar och radioastronomi.

”Keysights USPA-plattform accelererar och minskar riskerna vid chiputveckling, vilket ger en ny lösning som tar itu med utmaningarna med banbrytande design i högkostnadsmiljöer”, säger Dr. Joachim Peerlings, vice vd och chef för Keysights Network and Data Center Solutions Group. ”Denna kraftfulla plattform ger chiputvecklare en digital tvilling till sin framtida kiselenhet, vilket gör att de kan validera design och algoritmer fullt ut, vilket minimerar riskerna och kostnaderna i samband med omdesign.”

[annons_2]

Källänk

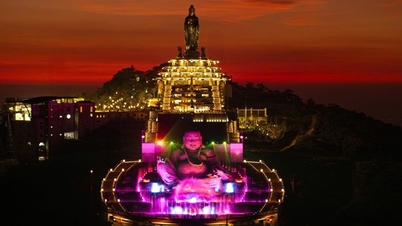

![[Foto] Tillbedjan av Tuyet Son-statyn – en nästan 400 år gammal skatt vid Keo-pagoden](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F02%2F1764679323086_ndo_br_tempimageomw0hi-4884-jpg.webp&w=3840&q=75)

![[Foto] Parad för att fira 50-årsdagen av Laos nationaldag](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F02%2F1764691918289_ndo_br_0-jpg.webp&w=3840&q=75)

Kommentar (0)