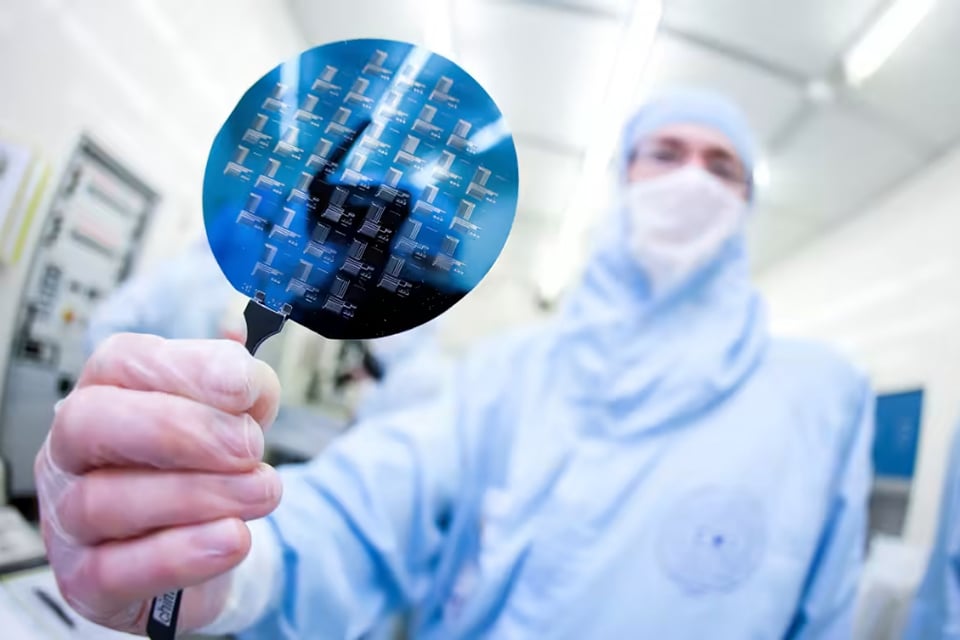

टॉम्स हार्डवेयर के अनुसार, 50,000 सिलिकॉन वेफर्स प्रति माह की क्षमता वाली 2एनएम चिप निर्माण सुविधा के निर्माण में निवेशकों को 28 बिलियन डॉलर की लागत आएगी, जबकि 3एनएम चिप्स के लिए इसी तरह की सुविधा के निर्माण के लिए 20 बिलियन डॉलर की आवश्यकता होगी।

2nm चिप्स के उत्पादन की बढ़ी हुई लागत का मतलब है कि ग्राहकों को अधिक भुगतान करना होगा।

इस लागत वृद्धि का कारण अत्यधिक महंगी एक्सट्रीम अल्ट्रावायलेट (ईयूवी) लिथोग्राफी मशीनों की बढ़ती मांग है। चिप निर्माताओं को अंततः इन लागतों को उत्पादन लागत में जोड़ना पड़ेगा, जिसके परिणामस्वरूप ग्राहकों के लिए कीमतें काफी बढ़ जाएंगी।

विशेष रूप से Apple के लिए, TSMC द्वारा निर्मित 2nm चिप वाले 300mm सिलिकॉन वेफर की कीमत $30,000 होगी, जबकि 3nm चिप वाले इसी तरह के वेफर की कीमत $20,000 होगी। TSMC के अन्य ग्राहकों के लिए इस तरह की कीमत की मांग करना अधिक कठिन होगा।

आईबीएस के विश्लेषकों का कहना है कि टीएसएमसी की 3एनएम प्रक्रिया से निर्मित प्रत्येक ए17 प्रो चिप की लागत लगभग 40 डॉलर होगी, लेकिन दोष दर के कारण एप्पल को प्रति चिप लगभग 50 डॉलर का भुगतान करना होगा। आईबीएस के अनुमान के अनुसार, 2एनएम चिप की उत्पादन लागत 60 डॉलर प्रति चिप होगी, जबकि एप्पल को लगभग 85 डॉलर प्रति चिप का भुगतान करना होगा।

कुछ पूर्व अनुमानों में 2nm चिप के लिए सिलिकॉन वेफर की कीमत 25,000 डॉलर बताई गई थी, इसलिए कीमत में काफी अंतर हो सकता है। बढ़ती लागत का सबसे ज्यादा असर मोनोलिथिक क्रिस्टल संरचनाओं के डेवलपर्स पर पड़ रहा है। मल्टी-चिप लेआउट अपनाने से लागत में काफी कमी आ सकती है, लेकिन इसके लिए उच्च गुणवत्ता वाली चिप पैकेजिंग की आवश्यकता होती है।

[विज्ञापन_2]

स्रोत लिंक

टिप्पणी (0)