チップ設計プロセスの最終段階であるシリコンテープアウトは、厳格でコストも高く、設計ミスが許容される余地はほとんどありません。テープアウト後に設計が失敗すると、チップメーカーは新たな「再設計」サイクルを開始しなければならず、その期間は12ヶ月以上に及ぶこともあります。この再設計によって生じる遅延は、追加の高額な研究開発リソースを必要とするだけでなく、チップメーカーが製品を予定通りに市場に投入できないことにもつながります。

Keysight Technologies は、幅広い測定およびテスト ソリューションを提供しています。

Keysight USPAプラットフォームは、チップ設計者やエンジニアに、チップ製造に移行する前に設計を検証するための完全な信号のデジタルツインを提供し、設計エラーのリスクと再設計コストを最小限に抑えます。USPAプラットフォームは、超高速信号コンバータと高性能FPGAプロトタイピングシステムを統合し、設計者に独自のカスタムプロトタイピングシステムに代わる選択肢を提供します。

さらに、このソリューションは、6G 無線アプリケーション開発、デジタル無線周波数メモリ、高度な物理学研究、レーダーや電波天文学などの高速データ取得アプリケーションなどのアプリケーションに適した入出力インターフェイスも提供します。

「キーサイトのUSPAプラットフォームは、チップ開発を加速し、リスクを軽減します。高コスト環境における最先端設計の課題に対処する革新的なソリューションを提供します」と、キーサイトのネットワークおよびデータセンターソリューショングループ担当副社長兼ゼネラルマネージャーであるヨアヒム・ピアリングス博士は述べています。「この強力なプラットフォームは、チップ開発者に将来のシリコンデバイスのデジタルツインを提供し、設計とアルゴリズムの完全な検証を可能にし、再設計に伴うリスクとコストを最小限に抑えます。」

[広告2]

ソースリンク

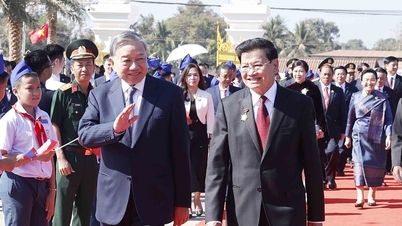

![[写真] ラオス建国記念日50周年を祝うパレード](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F02%2F1764691918289_ndo_br_0-jpg.webp&w=3840&q=75)

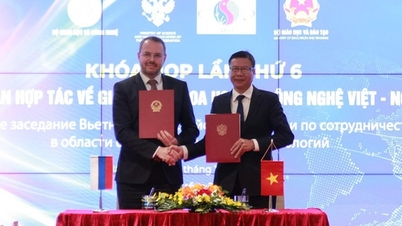

![[写真] ケオパゴダにある約400年前の宝物、トゥエットソン像を拝む](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F02%2F1764679323086_ndo_br_tempimageomw0hi-4884-jpg.webp&w=3840&q=75)

コメント (0)