Ini adalah inisiatif simbolik untuk menggalakkan kerjasama antara Jepun dan Korea Selatan dalam industri ini.

Sehubungan itu, kemudahan baharu itu akan menelan kos lebih daripada 30 bilion yen (222 juta USD), dijangka terletak di Yokohama, barat daya Tokyo, yang juga ibu pejabat semasa Institut Penyelidikan dan Pembangunan Samsung Jepun.

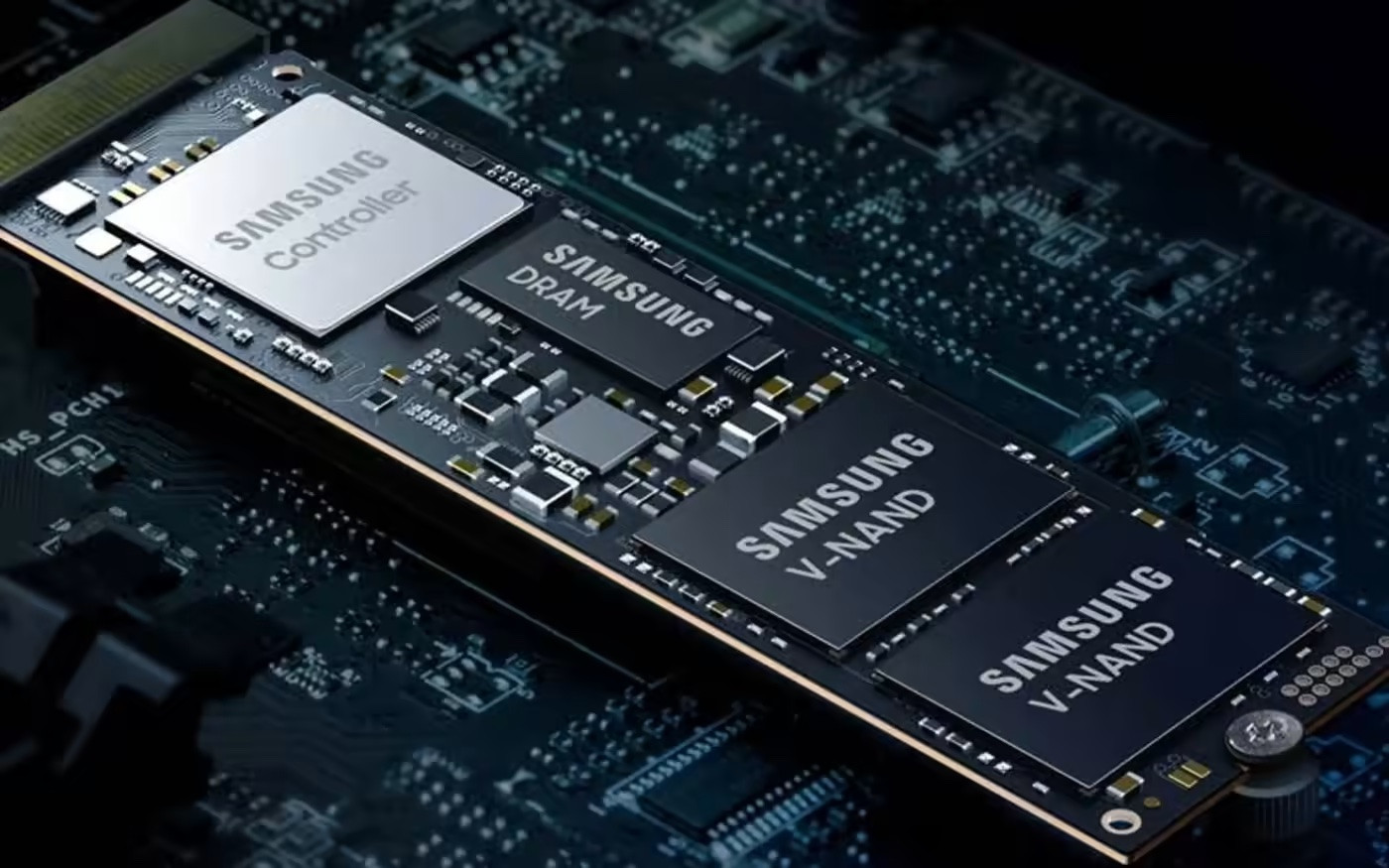

Samsung ialah pembuat cip memori terbesar di dunia , manakala Jepun ialah pengeluar utama bahan asas dalam semikonduktor, seperti wafer dan peralatan faundri.

Kemudahan baharu itu disasarkan untuk beroperasi menjelang 2025. Samsung sedang berusaha untuk mengambil kesempatan daripada subsidi berjumlah lebih daripada 10 bilion yen untuk sektor semikonduktor yang ditawarkan oleh kerajaan Jepun.

Langkah syarikat paling berharga Korea Selatan itu boleh merangsang lebih banyak kerjasama antara industri semikonduktor kedua-dua negara.

Pelaburan itu susulan perkongsian baharu antara Seoul dan Tokyo, diketuai oleh Presiden Korea Selatan Yoon Suk Yeol dan Perdana Menteri Jepun Fumio Kishida, yang dijangka bertemu di luar sidang kemuncak G7 di Hiroshima minggu depan.

Saingan utama Samsung TSMC juga membuat pelaburan besar di Jepun pada 2021, mempelbagaikan asas pembuatannya di tengah-tengah kebimbangan mengenai penumpuan berlebihan pengeluaran cip di Taiwan. TSMC juga mengekalkan kemudahan penyelidikan dan pembangunan di Tsukuba, timur laut Tokyo.

Jepun, yang pernah menjadi peneraju global dalam pengeluaran cip memori, cuba membina semula pangkalan pembuatannya dengan menarik pelaburan asing. TSMC dan Micron Technology adalah pelabur asing utama di Jepun dan telah menerima subsidi kerajaan.

Kemudahan baharu Samsung akan menumpukan pada bahagian belakang proses pembuatan semikonduktor, khususnya wafer pembungkusan yang telah disepadukan dengan papan litar ke dalam produk akhir.

Secara tradisinya, R&D telah menumpukan pada peringkat awal proses pembuatan, bertujuan untuk mengecilkan litar sebanyak mungkin. Tetapi ramai yang percaya terdapat had untuk pengecilan selanjutnya, dan tumpuan akan beralih kepada menambah baik proses belakang, seperti menyusun wafer semikonduktor ke dalam berbilang lapisan untuk mencipta cip 3D.

(Menurut NikkeiAsia)

Sumber

![[Foto] Perdana Menteri Pham Minh Chinh bertemu dengan wakil guru cemerlang](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/15/1763215934276_dsc-0578-jpg.webp)

![[Foto] Panorama Pusingan Akhir Anugerah Tindakan Komuniti 2025](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/15/1763206932975_chi-7868-jpg.webp)

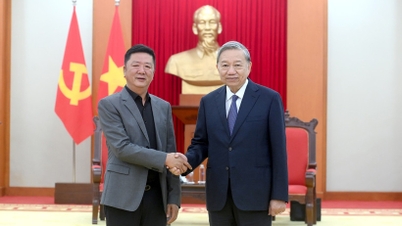

![[Foto] Setiausaha Agung Lam menerima Naib Presiden Kumpulan Luxshare-ICT (China)](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/15/1763211137119_a1-bnd-7809-8939-jpg.webp)

Komen (0)