Dies ist eine symbolische Initiative zur Förderung der Zusammenarbeit zwischen Japan und Südkorea in dieser Branche.

Demnach wird die neue Anlage mehr als 30 Milliarden Yen (222 Millionen USD) kosten und soll in Yokohama, südwestlich von Tokio, errichtet werden, wo sich auch der derzeitige Hauptsitz des Samsung Research and Development Institute Japan befindet.

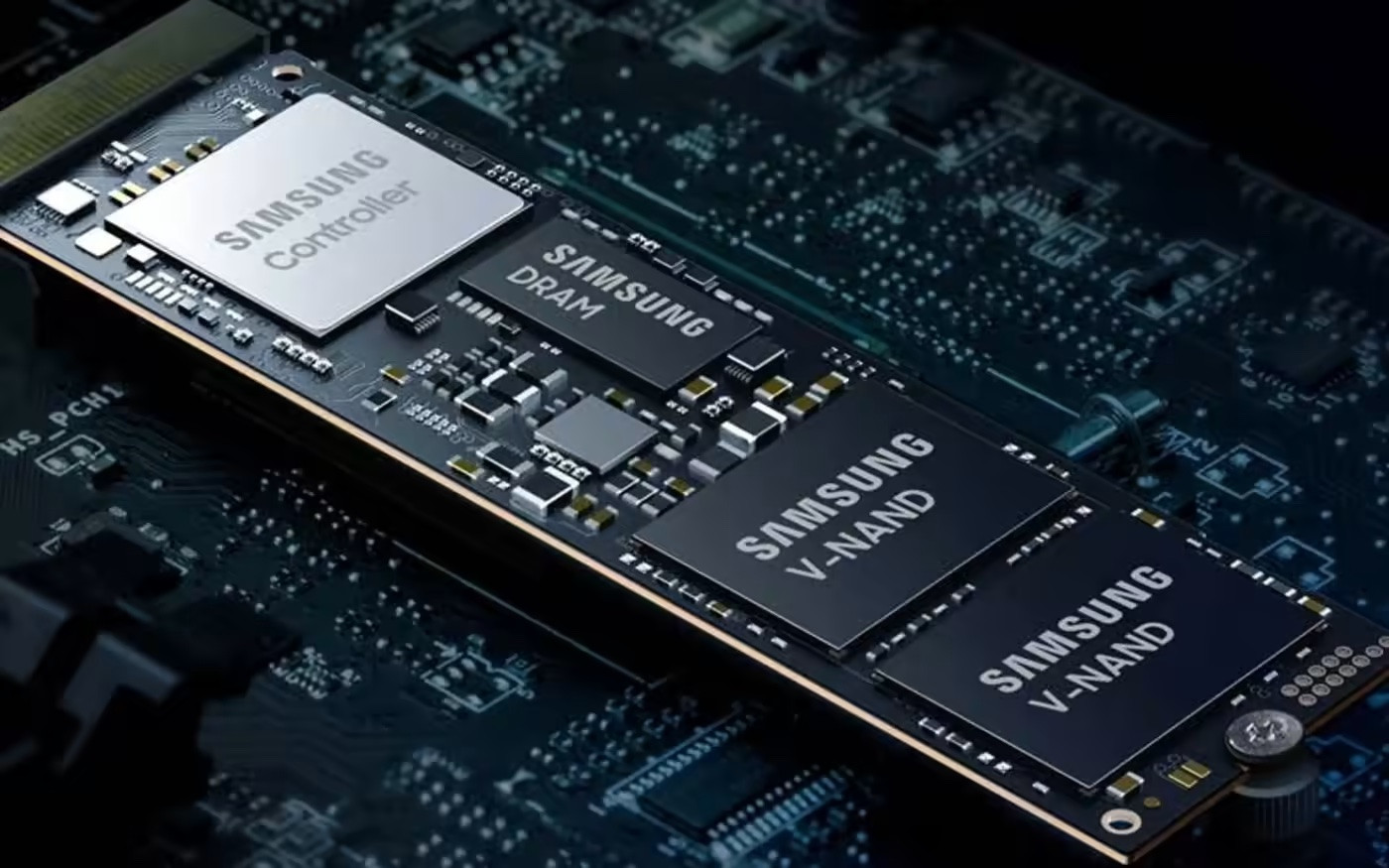

Samsung ist der weltweit größte Hersteller von Speicherchips, während Japan ein führender Produzent von Basismaterialien für Halbleiter ist, wie z. B. Wafer und Gießereianlagen.

Die neue Anlage soll bis 2025 in Betrieb gehen. Samsung möchte die von der japanischen Regierung angebotenen Subventionen für den Halbleitersektor in Höhe von insgesamt mehr als 10 Milliarden Yen nutzen.

Der Schritt des wertvollsten Unternehmens Südkoreas könnte eine engere Zusammenarbeit zwischen den Halbleiterindustrien beider Länder anregen.

Die Investition folgt einer neuen Partnerschaft zwischen Seoul und Tokio unter der Führung des südkoreanischen Präsidenten Yoon Suk Yeol und des japanischen Premierministers Fumio Kishida, die sich voraussichtlich nächste Woche am Rande des G7-Gipfels in Hiroshima treffen werden.

Samsungs größter Konkurrent TSMC investierte 2021 ebenfalls massiv in Japan und diversifizierte damit seine Produktionsbasis angesichts der Bedenken hinsichtlich einer zu starken Konzentration der Chip-Produktion in Taiwan. TSMC unterhält zudem ein Forschungs- und Entwicklungszentrum in Tsukuba, nordöstlich von Tokio.

Japan, einst weltweit führend in der Speicherchip-Produktion, versucht, seine Produktionsbasis durch die Anwerbung ausländischer Investitionen wieder aufzubauen. TSMC und Micron Technology gehören zu den größten ausländischen Investoren in Japan und erhalten staatliche Subventionen.

Die neue Anlage von Samsung wird sich auf den Back-End-Bereich des Halbleiterherstellungsprozesses konzentrieren, insbesondere auf das Verpacken von Wafern, die mit Leiterplatten zu Endprodukten integriert wurden.

Traditionell konzentrierte sich die Forschung und Entwicklung auf die frühen Phasen des Fertigungsprozesses mit dem Ziel, Schaltkreise so weit wie möglich zu verkleinern. Viele sind jedoch der Ansicht, dass die Miniaturisierung Grenzen hat und der Fokus sich künftig auf die Verbesserung von Folgeprozessen verlagern wird, beispielsweise auf das Stapeln von Halbleiterwafern in mehreren Lagen zur Herstellung von 3D-Chips.

(Laut NikkeiAsia)

Quelle

![[Foto] Generalsekretär To Lam und der Vorsitzende der Nationalversammlung, Tran Thanh Man, nehmen an der Feier zum 80. Jahrestag des traditionellen Tages des vietnamesischen Inspektionssektors teil.](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/17/1763356362984_a2-bnd-7940-3561-jpg.webp)

Kommentar (0)