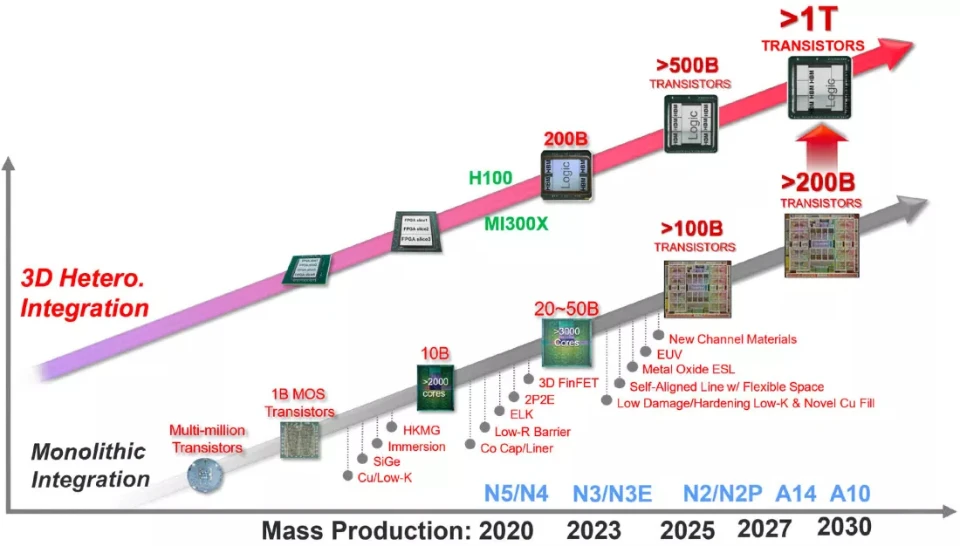

Menurut Techspot , di persidangan IEDM baru-baru ini, TSMC mengumumkan pelan tindakan produk untuk proses pembuatan semikonduktor generasi akan datang, yang akhirnya menawarkan koleksi reka bentuk ciplet bertindan 3D dengan 1 trilion transistor setiap pakej cip tunggal. Kemajuan dalam teknologi pembungkusan, seperti CoWoS, InFO dan SoIC, akan membolehkan syarikat mencapai matlamat tersebut, dan menjelang 2030, TSMC percaya reka bentuk monolitiknya boleh mencapai 200 bilion transistor.

TSMC percaya ia boleh menghasilkan cip 1nm menjelang 2030.

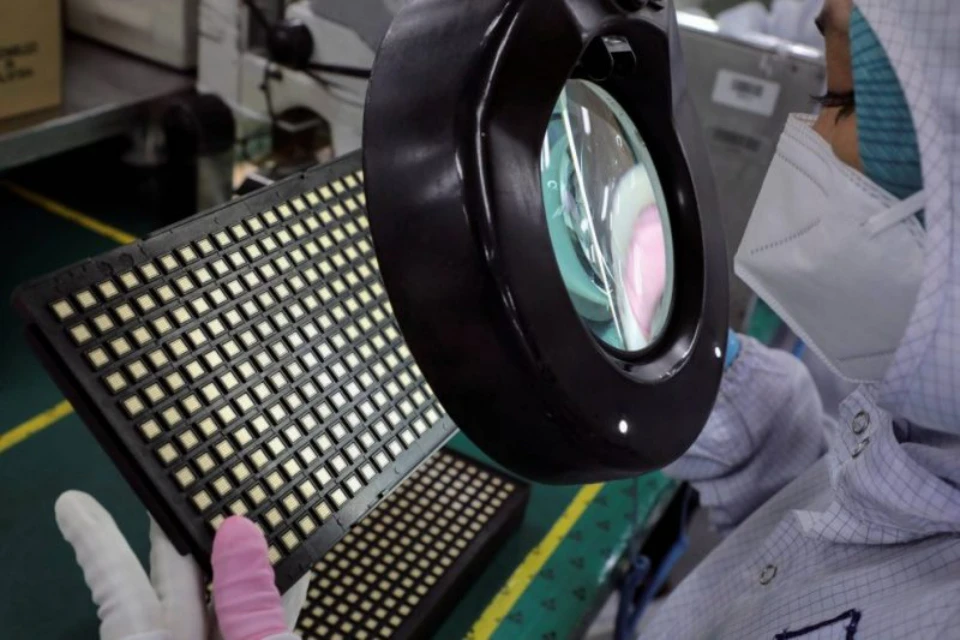

GH100 Nvidia, dengan 80 bilion transistornya, merupakan salah satu cip monolitik paling kompleks yang ada di pasaran pada masa ini. Walau bagaimanapun, memandangkan saiz cip ini terus meningkat dan menjadi lebih mahal, TSMC percaya bahawa pengeluar akan menerima pakai seni bina berbilang cip, seperti Instinct MI300X AMD yang baru dilancarkan dan Ponte Vecchio Intel, yang mempunyai 100 bilion transistor.

Pada masa ini, TSMC akan terus membangunkan proses pembuatan 2nm N2 dan N2P, serta cip 1.4nm A14 dan 1nm A10. Syarikat itu menjangkakan akan memulakan pengeluaran 2nm menjelang akhir tahun 2025. Pada tahun 2028, mereka akan beralih kepada proses 1.4nm A14, dan menjelang 2030, mereka dijangka akan menghasilkan transistor 1nm.

Sementara itu, Intel sedang mengusahakan proses 2nm (20A) dan 1.8nm (18A), yang dijangka dilancarkan dalam tempoh masa yang sama. Satu kelebihan teknologi baharu ini ialah ia menawarkan ketumpatan logik yang lebih tinggi, kelajuan jam yang lebih tinggi dan kebocoran kuasa yang lebih rendah, menghasilkan reka bentuk yang lebih cekap tenaga.

Matlamat TSMC untuk membangunkan cip canggih generasi akan datang.

Sebagai faundri terbesar di dunia , TSMC yakin proses pembuatannya akan mengatasi mana-mana produk Intel. Dalam panggilan persidangan pelaporan kewangan, Ketua Pegawai Eksekutif TSMC, CC Wei, menyatakan bahawa penilaian dalaman mengesahkan penambahbaikan dalam teknologi N3P dan proses pembuatan 3nm syarikat, membuktikan "PPAnya setanding" dengan proses 18A Intel. Beliau menjangkakan N3P akan menjadi lebih baik, lebih berdaya saing dan menawarkan kelebihan kos yang ketara.

Sementara itu, Ketua Pegawai Eksekutif Intel, Pat Gelsinger mendakwa proses pembuatan 18A mereka akan mengatasi cip 2nm TSMC yang dilancarkan setahun sebelumnya. Sudah tentu, hanya masa yang akan menentukan.

[iklan_2]

Pautan sumber

![[Imej] Imej yang bocor menjelang majlis gala Anugerah Tindakan Komuniti 2025.](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F16%2F1765882828720_ndo_br_thiet-ke-chua-co-ten-45-png.webp&w=3840&q=75)

![[Foto] Perdana Menteri Pham Minh Chinh menerima kunjungan Gabenor Wilayah Tochigi (Jepun)](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F16%2F1765892133176_dsc-8082-6425-jpg.webp&w=3840&q=75)

![[Foto] Perdana Menteri Pham Minh Chinh menerima kunjungan Menteri Pendidikan dan Sukan Laos, Thongsalith Mangnormek](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F16%2F1765876834721_dsc-7519-jpg.webp&w=3840&q=75)

![[Langsung] Gala Anugerah Tindakan Komuniti 2025](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F16%2F1765899631650_ndo_tr_z7334013144784-9f9fe10a6d63584c85aff40f2957c250-jpg.webp&w=3840&q=75)

Komen (0)