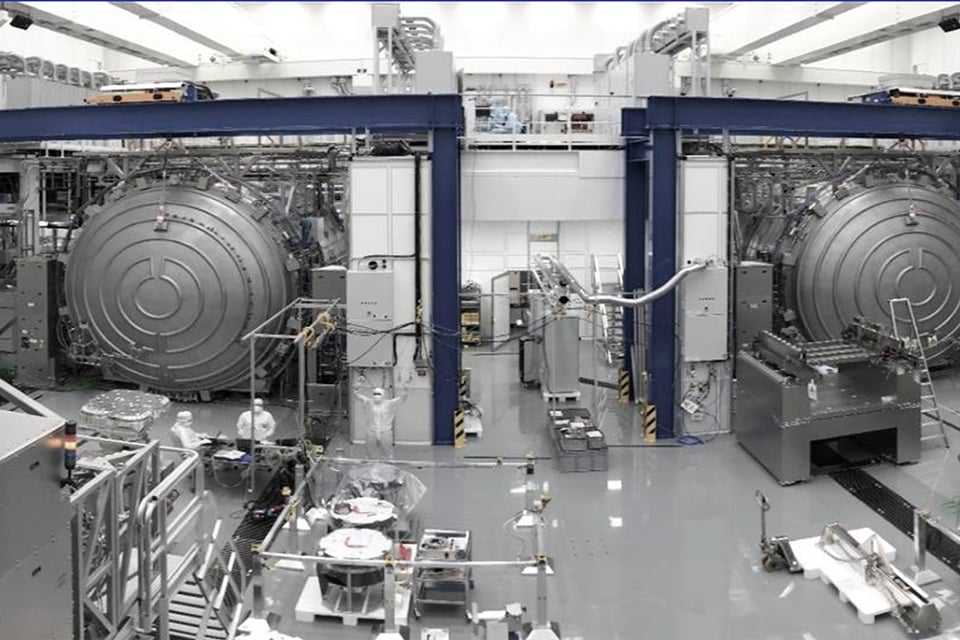

Laut PhoneArena werden TSMC und Samsung Foundry voraussichtlich 2025 mit der Massenproduktion von 2-nm-Chips beginnen. Dies bedeutet, dass Intel mit 1,8-nm-Chips die Führung bei den Chipfertigungsprozessen übernehmen kann. Intel soll zwischen 300 und 400 Millionen US-Dollar pro EUV-High-NA-Maschine investieren.

Jede ASML High-NA-Maschine kostet mindestens 300 Millionen Dollar.

„Wir liefern das erste High-NA-System aus und haben dies in einem Social-Media-Beitrag bekannt gegeben. Das System wird wie geplant und bereits angekündigt an Intel geliefert“, erklärte ASML zu dem Transfer.

Bei einem High-NA-System gilt: Je höher die NA-Zahl, desto höher die Auflösung des auf den Siliziumwafer geätzten Musters. Während aktuelle EUV-Anlagen eine Apertur von 0,33 (entspricht einer Auflösung von 13 nm) aufweisen, besitzt eine High-NA-Anlage eine Apertur von 0,55 (entspricht einer Auflösung von 8 nm). Durch die Übertragung des höher aufgelösten Musters auf den Wafer muss die Foundry den Wafer möglicherweise nicht zweimal durch die EUV-Anlage laufen lassen, um zusätzliche Strukturen hinzuzufügen. Dies spart Zeit und Kosten.

EUV-Laser mit hoher numerischer Apertur (NA) zielen hauptsächlich darauf ab, die Größe von Transistoren zu reduzieren und deren Dichte zu erhöhen, um mehr Transistoren auf einem Chip unterzubringen. Je höher die Anzahl der Transistoren auf einem Chip ist, desto leistungsstärker und energieeffizienter ist er. Mit High-NA-Lasern lassen sich Transistoren um den Faktor 1,7 verkleinern, während die Dichte um das 2,9-Fache steigt.

Jede High-NA-Maschine wird von ASML in 13 großen Containern versendet.

Die neue Version der EUV-Anlage mit hoher numerischer Apertur (NA) wird die Herstellung von Chips mit 2 nm Strukturgröße und darunter ermöglichen. Erst letzte Woche stellten TSMC und Samsung Foundry ihre Roadmap für die Zeit nach der 2-nm-Phase vor. Die beiden Unternehmen planen, bis 2027 Halbleiter im 1,4-nm-Verfahren zu entwickeln. Die Produktion von 2-nm-Chips soll voraussichtlich 2025 beginnen, und vor wenigen Tagen erlaubte TSMC Apple die Evaluierung von 2-nm-Chip-Prototypen.

Der Transport der EUV-Hoch-NA-Maschine war keine leichte Aufgabe, da sie in 13 große Container und 250 Kisten zerlegt werden musste. Auch die Montage der Maschine gestaltete sich äußerst schwierig.

Quellenlink

![[Foto] Cat Ba – Grünes Inselparadies](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F04%2F1764821844074_ndo_br_1-dcbthienduongxanh638-jpg.webp&w=3840&q=75)

![[VIMC 40 Tage Blitzgeschwindigkeit] Der Hafen von Hai Phong ist entschlossen, den Durchbruch zu schaffen und das Ziel von 2 Millionen TEU bis 2025 zu erreichen.](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/12/04/1764816441820_chp_4-12-25.jpeg)

Kommentar (0)