PhoneArenaによると、TSMCとSamsung Foundryは2025年に2nmチップの量産を開始する予定で、これは1.8nmチップによってIntelがチップ製造プロセスでリードすることを意味します。IntelはEUV High-NA装置1台あたり3億ドルから4億ドルを投資すると言われています。

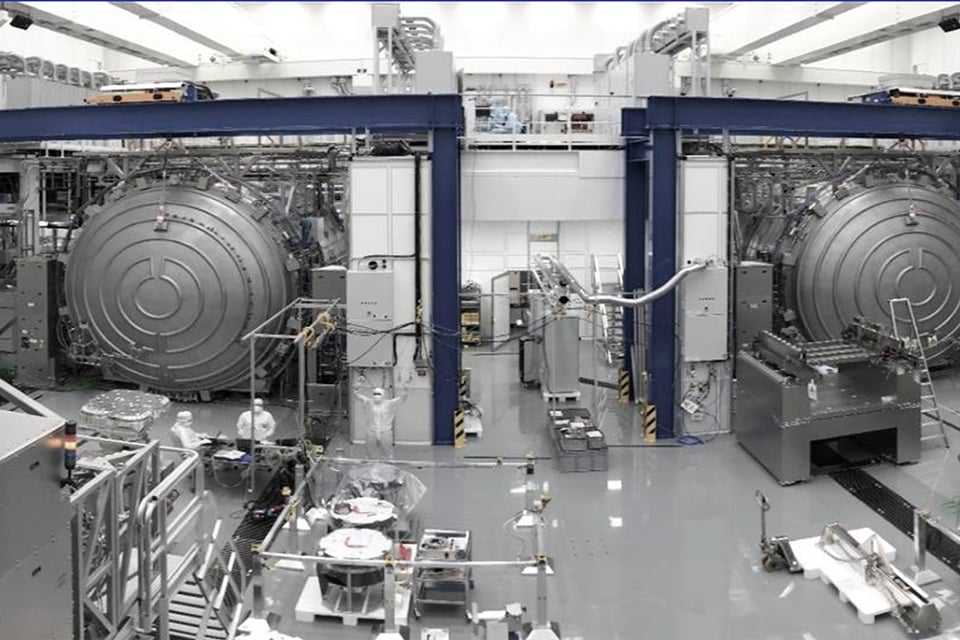

ASML の High-NA マシン 1 台あたりのコストは少なくとも 3 億ドルです。

ASMLは今回の移管について、「当社は最初の高NAシステムを出荷しており、ソーシャルメディアの投稿で発表しました。システムは、以前発表した通り、計画通りインテルに納入されます」と述べた。

高NAシステムでは、NA値が高いほど、シリコンウェーハにエッチングされるパターンの解像度が高くなります。現在のEUV装置の開口数は0.33(13nmの解像度に相当)ですが、高NA装置は開口数が0.55(8nmの解像度に相当)です。より高解像度のパターンがウェーハに転写されるため、ファウンドリは追加機能を追加するためにウェーハをEUV装置に2回通す必要がなくなり、時間とコストの両方を節約できます。

高NA EUV装置は、トランジスタのサイズを縮小し、チップ内により多くのトランジスタを詰め込むための高密度化に主眼を置いています。チップ上のトランジスタ数が多いほど、チップの性能とエネルギー効率は向上します。高NA装置では、トランジスタを1.7倍縮小し、高密度化を2.9倍に高めることができます。

各高NAマシンはASMLによって13個の大型コンテナで出荷される。

高NA EUV装置の新バージョンは、2nm以下のチップ製造の実現に貢献します。先週、TSMCとSamsung Foundryはポスト2nmロードマップを発表しました。両社は2027年までに1.4nmプロセスを採用した半導体を開発する計画です。2nmチップの生産は2025年に開始される予定で、数日前にはTSMCがAppleに2nmチップのプロトタイプ評価を許可しました。

EUV高開口数装置は13個の大型コンテナと250個の木箱に分割されていたため、輸送は容易ではありませんでした。装置の組み立ても非常に困難でした。

[広告2]

ソースリンク

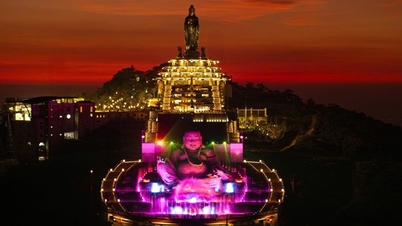

![[写真] ケオパゴダにある約400年前の宝物、トゥエットソン像を拝む](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F02%2F1764679323086_ndo_br_tempimageomw0hi-4884-jpg.webp&w=3840&q=75)

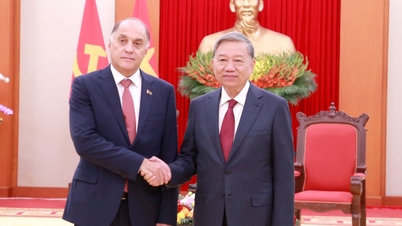

![[写真] ラオス建国記念日50周年を祝うパレード](/_next/image?url=https%3A%2F%2Fvphoto.vietnam.vn%2Fthumb%2F1200x675%2Fvietnam%2Fresource%2FIMAGE%2F2025%2F12%2F02%2F1764691918289_ndo_br_0-jpg.webp&w=3840&q=75)

コメント (0)