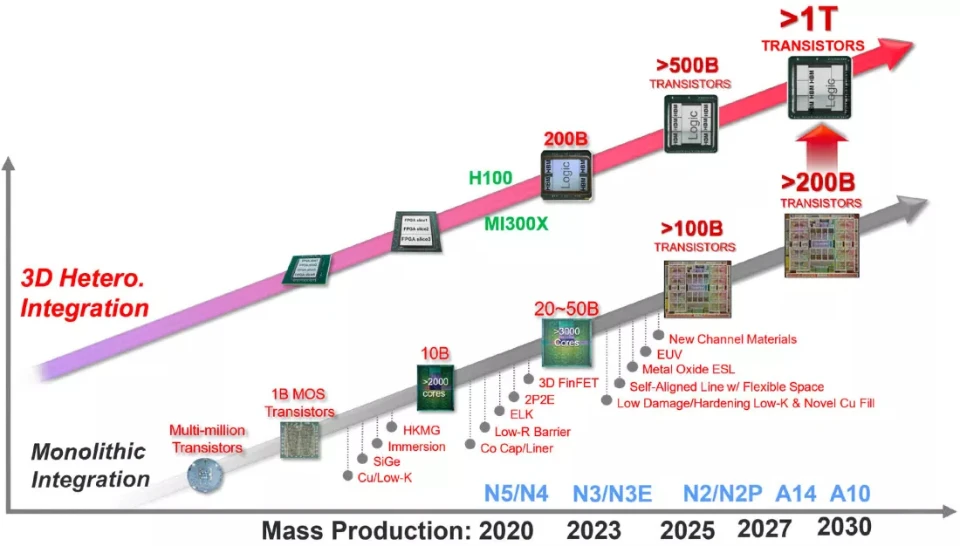

Selon Techspot , lors de la récente conférence IEDM, TSMC a annoncé sa feuille de route pour ses procédés de fabrication de semi-conducteurs de nouvelle génération. Celle-ci permettra à terme de proposer des puces monolithiques 3D empilées intégrant 1 000 milliards de transistors. Les progrès réalisés dans les technologies d'encapsulation telles que CoWoS, InFO et SoIC permettront à l'entreprise d'atteindre cet objectif. TSMC estime que d'ici 2030, ses puces monolithiques pourraient intégrer jusqu'à 200 milliards de transistors.

TSMC estime pouvoir créer des puces de 1 nm d'ici 2030.

La puce GH100 de Nvidia, composée de 80 milliards de transistors, est l'une des puces monolithiques les plus complexes du marché. Cependant, face à la croissance continue de la taille et du coût de ces puces, TSMC estime que les fabricants adopteront des architectures multi-chiplets, telles que l'Instinct MI300X d'AMD, récemment lancée, et la Ponte Vecchio d'Intel, qui compte 100 milliards de transistors.

Pour l'instant, TSMC poursuit le développement de ses procédés de fabrication 2 nm N2 et N2P, ainsi que des puces 1,4 nm A14 et 1 nm A10. L'entreprise prévoit de démarrer la production en 2 nm d'ici fin 2025. En 2028, elle passera au procédé 1,4 nm A14 et, d'ici 2030, elle espère produire des transistors 1 nm.

Parallèlement, Intel travaille sur des procédés de gravure de 2 nm (20A) et de 1,8 nm (18A), dont le lancement est prévu simultanément. L'un des avantages de cette nouvelle technologie réside dans sa densité logique accrue, ses fréquences d'horloge plus élevées et son courant de fuite réduit, permettant ainsi des conceptions plus économes en énergie.

L'objectif de TSMC est de développer la prochaine génération de puces avancées.

En tant que premier fondeur mondial , TSMC est convaincu que ses procédés de fabrication surpasseront tous les produits Intel. Lors d'une conférence téléphonique sur les résultats, le PDG de TSMC, CC Wei, a déclaré que des audits internes avaient confirmé les améliorations apportées à la technologie N3P et que le procédé de fabrication 3 nm de l'entreprise s'avérait « comparable en termes de performances, de puissance et de surface » (PPA) au procédé 18A d'Intel. Il prévoit que la technologie N3P sera encore plus performante, plus compétitive et offrira un avantage concurrentiel significatif en termes de coûts.

Parallèlement, le PDG d'Intel, Pat Gelsinger, affirme que leur procédé de fabrication 18A surpassera les puces 2 nm de TSMC sorties un an plus tôt. Seul l'avenir nous le dira.

Lien source

![[Photo] Le Premier ministre Pham Minh Chinh rencontre des représentants d'enseignants exceptionnels](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/15/1763215934276_dsc-0578-jpg.webp)

![[Photo] Panorama de la finale des Community Action Awards 2025](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/15/1763206932975_chi-7868-jpg.webp)

![[Photo] Le secrétaire général To Lam reçoit le vice-président du groupe Luxshare-ICT (Chine)](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/11/15/1763211137119_a1-bnd-7809-8939-jpg.webp)

Comment (0)